Arrays – VHDL Example

Create your own types using arrays.

Arrays are used in VHDL to create a group of elements of one data type. Arrays can only be used after you have created a special data type for that particular array. Below are some rules about arrays.

- Arrays can be synthesized

- Arrays can be initialized to a default value

- Array type definitions can be unconstrained (undefined length)

- Arrays of arrays are allowed (e.g. an array of std_logic_vector)

- Two-Dimensional (2D) arrays are allowed

- Signals and Variables can be declared as an array type

Creating An Array:

Initializing an array:, creating a two-dimensional (2d) array.

Learn Verilog

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

courses:system_design:vhdl_language_and_syntax:extended_data_types:arrays

More Arrays

- Constrained or unconstrained size

- Range specification necessary

- The index set can be of any type

Arrays are a collection of a number of values of a single data type and are represented as a new data type in VHDL.

It is possible to leave the range of array indices open at the time of definition. These so called unconstrained arrays can not be used as signals, however, i.e. the index range has to be specified in the signal declaration then. The advantage of unconstrained arrays is the possibility to concatenate objects of different lengths, for example, because they are still of the same data type.

This would not be allowed if each array length was declared as separate data type. VHDL does not put any restrictions on the index set of arrays, as long it is a discrete range of values. It is even legal to use enumeration types, as shown in the code example, although this version is not generally synthesizable.

Multidimensional Array

- Array of array

- Multidimensional array

- Different referencing

- Barely supported by synthesis tools

Multidimensional arrays can simply be obtained by defining a new data type as array of another array data type (1). When accessing its array elements, the selections are processed from left to right, i.e. the leftmost pair of brackets selects the index range for the “outermost” array. Thus ’MATRIX_3x8(2)’ selects the second ’INTEGER_VECTOR’ of ’MATRIX_A’.

The range enclosed in the next pair applies to the array that is returned by the previous slice selection, i.e. ’MATRIX_3x8(2)(4)’ returns the fourth integer value of this ’INTEGER_VECTOR’. Multiple dimensions can also be specified directly within a new array definition (2). The ranges of the different dimensions are separated by ’,’ symbols. If a whole row or column is to be selected, the range has to be provided in the slice selection. Multidimensional arrays are generally synthesizable up to dimension 2, only.

Aggregates and Multidimensional Arrays

- Aggregates may be nested

- Aggregates can be used to make assignments to all elements of a multidimensional array

The most convenient way to assign values to multiple array elements is via the aggregate mechanism. Aggregates can also be nested for this purpose. With an aggregate one can assign to all elements of an array a specific value in a clear fashion.

Chapters of System Design > VHDL Language and Syntax > Extended Data Types

- Introduction

- Standard Logic Type

- Enumeration Types

Chapters of System Design > VHDL Language and Syntax

- General Issues

- VHDL Structural Elements

- Process Execution

- Extended Data Types

- Sequential Statements

- Subprograms

- Subprogram Declaration and Overloading

- Concurrent Statements

Arrays – VHDL Example

Create your own kinds using arrays.

Arrays are used is VHDL to create a group of elements of of data type. Arrays can only be previously after you have created a special data type for that extra array. Below are some rules about arrays. Locate few example with how up declare and array includes VHDL. The VHDL Fields reference syntax and VHDL Array initialization. One and Multi-dimensional VHDL array

- Arrays can be synthesized

- Arrays can be initialized to a default value

- Array type definitions can be unconstrained (undefined length)

- Arrays of arrays were permissible (e.g. an array of std_logic_vector)

- Two-Dimensional (2D) arrays are allowed

- Signals and Variables can be declared as an array type

Creating An Array:

Initializing an array:, creating a two-dimensional (2d) array.

Learn Verilog

Leave ADENINE Comment Cancel reply

Save insert name, mail, and company in this browser for the following time I comment.

404 Not found

Most logic synthesis tools accept one-dimensional arrays of other supported types. 1-D arrays of 1-D arrays are often supported. Some tols also allow true 2-D arrays, but not more dimensions.

Note that arrays are usually implemented using gates and flip-flops, not ROM's and RAM's.

Array types have not changed in VHDL -93.

Eze (Member) asked a question.

Which of the following two approaches is favored by the tools:

a. Array of array:

- type MEM_ROW_TYPE is array ( 0 to MEM_DEPTH - 1 ) of std_logic_vector ( DATA_WIDTH - 1 downto 0 );

- type MEM_TYPE is array ( 0 to 2 ** CHANNEL_WIDTH - 1 ) of MEM_ROW_TYPE ;

- signal ram : MEM_TYPE ;

- ram ( row )( col ) <= write_data_in ;

- read_data_out <= ram ( row )( col );

b. Two dimensional array

- type MEM_TYPE is array ( 0 to 2 ** CHANNEL_WIDTH - 1 , 0 to MEM_DEPTH - 1 ) of std_logic_vector ( DATA_WIDTH - 1 downto 0 );

- ram ( row , col ) <= write_data_in ;

- read_data_out <= ram ( row , col );

drjohnsmith (Member)

Try a test setup

ensure you set the VHDL to 2008 though

And , if you have this in a test bench,

and you want to use post P&R simulation,

the tools will have re arranged this as std_logic (vector)

https://support.xilinx.com/s/question/0D52E00006hpXF9SAM/arrays-as-ports-in-vhdl

Tricky (Member)

@drjohnsmith (Member) 2008 not needed. Both code examples are VHDL 1993 code.

@Eze (Member) While both are legal, neither will infer a RAM in Vivado. You need to use a 1d array to infer a ram. So you will need to do the following:

- type ram_t is array ( 0 to MEM_DEPTH * ( 2 ** CHANNEL_WIDTH ) - 1 ) of std_logic_vector ( DW - 1 downto 0 )

- signal ram : ram_t ;

- -- in a clocked process etc , following synthesis template

- ram ( to_integer ( row & column )) <= din ;

- dout <= ram ( to_integer ( row & column ));

You must ensure that each row is 2**N entries long.

The last time I tried, Vivado will not even infer rams when the source is a 1dx1d array, and each array is a valid ram inference template inside a generate loop. Each ram can be ONLY a 1D array, hence you have to declare the arrays inside the generate loop.

My apologies,

I read it as needing two dimensional ports,

https://www.nandland.com/vhdl/examples/example-array-type-vhdl.html

Inferring rams is / has always been "interesting"

its very easy to code a way that to us is a ram, to the tools is a bunch of registers.

Xilinx provide a set of template and discussion on options in there guide UG901

There might be a newer one than this

https://www.xilinx.com/support/documentation/sw_manuals/xilinx2018_3/ug901-vivado-synthesis.pdf

I'd strongly suggest that you isolate the ram into a single entity

and experiment to check it goes into what you expect.

And I'd always recommend setting 2008 in VHDL unless you defiantly have reason to use a 1993 code style that does not work in 2008

Eze (Member)

Thanks Tricky and drjohnsmith for your responses!

drjohnsmith , the 2D Array in the Nandland example is exactly the definition I presented in my second approach. As Tricky noted, the problem with this definition is that it does not infer RAM.

I am currently trying the following implementation which instantiates 256 dprams of 256x64b each one:

- ram_per_channel : for i in 0 to 255 generate

- rambuffer : entity work . ram_dp

- generic map (

- DATA_WIDTH => 64 ,

- ADDR_WIDTH => 8 )

- clk => clk ,

- raddr => ram_read_addr ( i ),

- waddr => ram_write_addr ( i ),

- data => ram_write_data ( i ),

- we => ram_write_enable ( i ),

- q => ram_read_data ( i )

- end generate ;

I use a custom VHDL entity for the DPRAM as follows:

- subtype word_t is std_logic_vector (( DATA_WIDTH - 1 ) downto 0 );

- type memory_t is array ( 2 ** ADDR_WIDTH - 1 downto 0 ) of word_t ;

- signal ram : memory_t ;

- process ( clk )

- if ( rising_edge ( clk )) then

- if ( we = '1' ) then

- ram ( to_integer ( unsigned ( waddr ))) <= data ;

- q <= ram ( to_integer ( unsigned ( raddr )));

- end process ;

Which seems to work except that it doesn't infer BRAM as I would expec t. Any words of wisdom?

Correction: this last implementation does infer BRAM

@Eze (Member)

thanks for the feedback

I have used NandLand for many years,

I'll try to remember that its not infallible

and till xilinx break it, try to link to this answer of yours,

Related Questions

Community Feedback?

404 Not found

What is an array

In any software programming language, when we need to deal with a collection of elements of the same type we can take advantage of the dedicated data structures provided by the language. In VHDL such kind of structure is defined “ array “.

We can collect any data type object in an array type, many of the predefined VHDL data types are defined as an array of a basic data type.

An example is:

VHDL array declaration

The VHDL Arrays can be may both one-dimensional (with one index) or multidimensional (with two or more indices).

When we declare an array, we can decide if the array is

- Constrained

- Urnconstrained

In the constrained array, he bounds for an index are established when the array type is defined

In the unconstrained array, the bounds are established subsequently during the declaration of the variable or signal.

The BNF for declaring an array type is:

the subtype allows the values taken on by an object to be restricted or constrained subset of some base type.

Some examples of constrained array type declarations:

Accessing to the array object

An element of an array object can be referred to by indexing the name of the object.

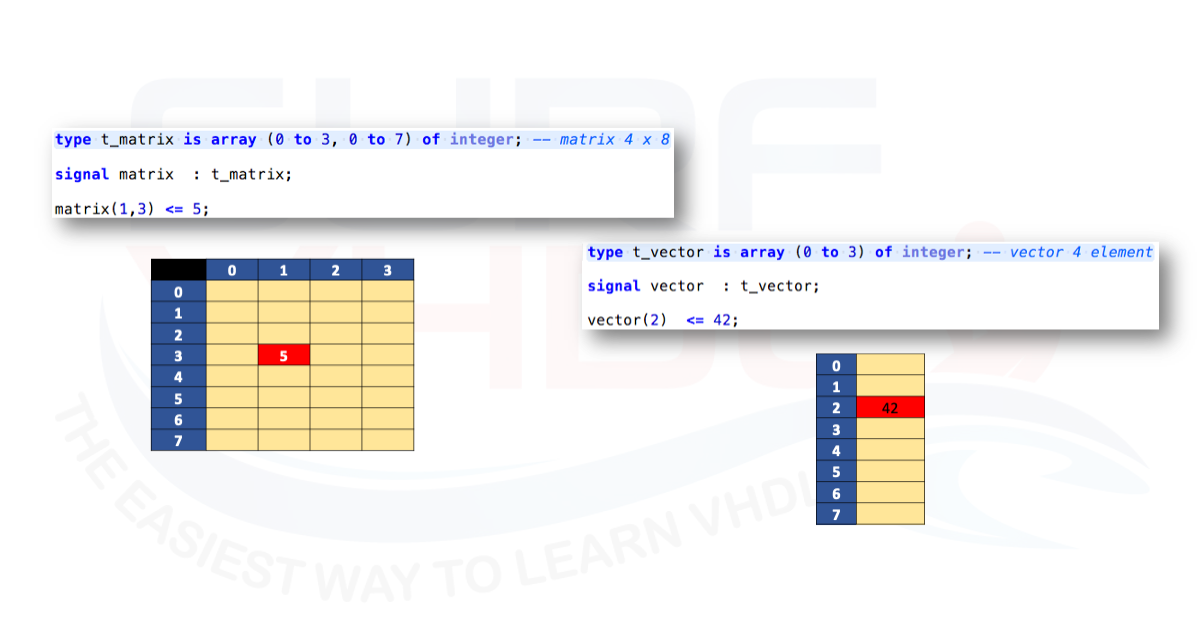

Figure 1 reports an example of the signal vector and matrix addressing, here below the VHDL code for matrix and vector definition and addressing.

Implementing a MUX using an array in VHDL

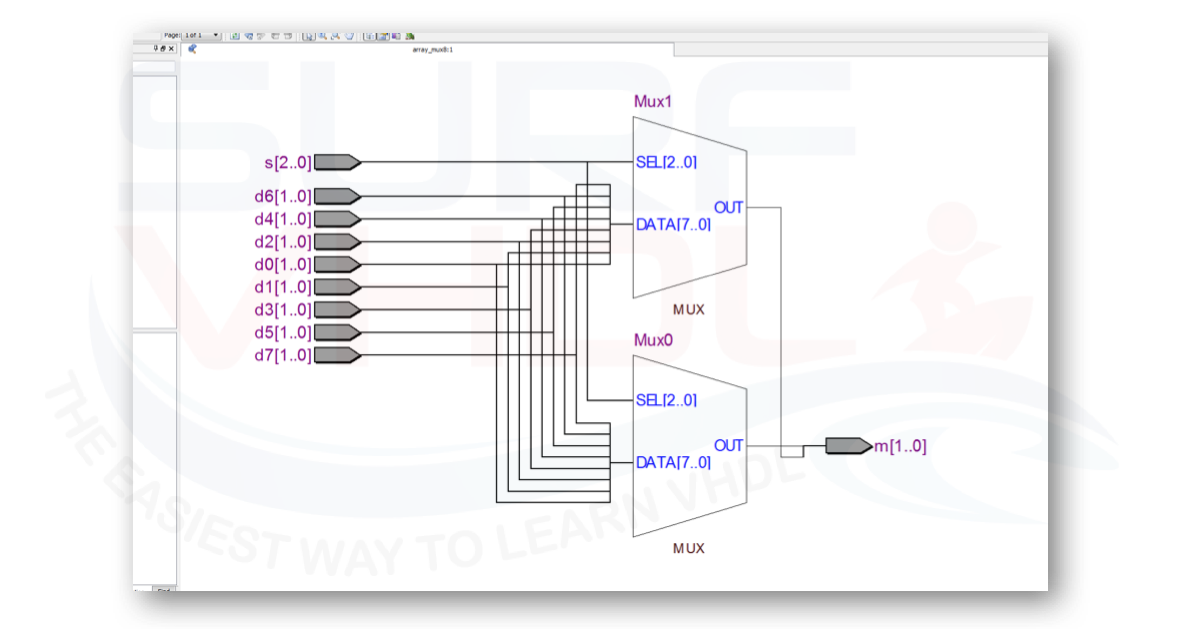

In this post, we describe the VHDL implementation of a MUX using the CASE-WHEN statement . Another compact and elegant way for describing a MUX architecture in VHDL is to use the array approach. In the VHDL code below is reported the VHDL code of the implementation of an 8-way MUX. We defined an array of the same type of data of the MUX then the array is referenced using the MUX selector. In a single VHDL line, we can implement an N-way MUX.

As example, Figure 2 shows the RTL view of the 8-way MUX implementation on Altera/Intel Cyclone II FPGA

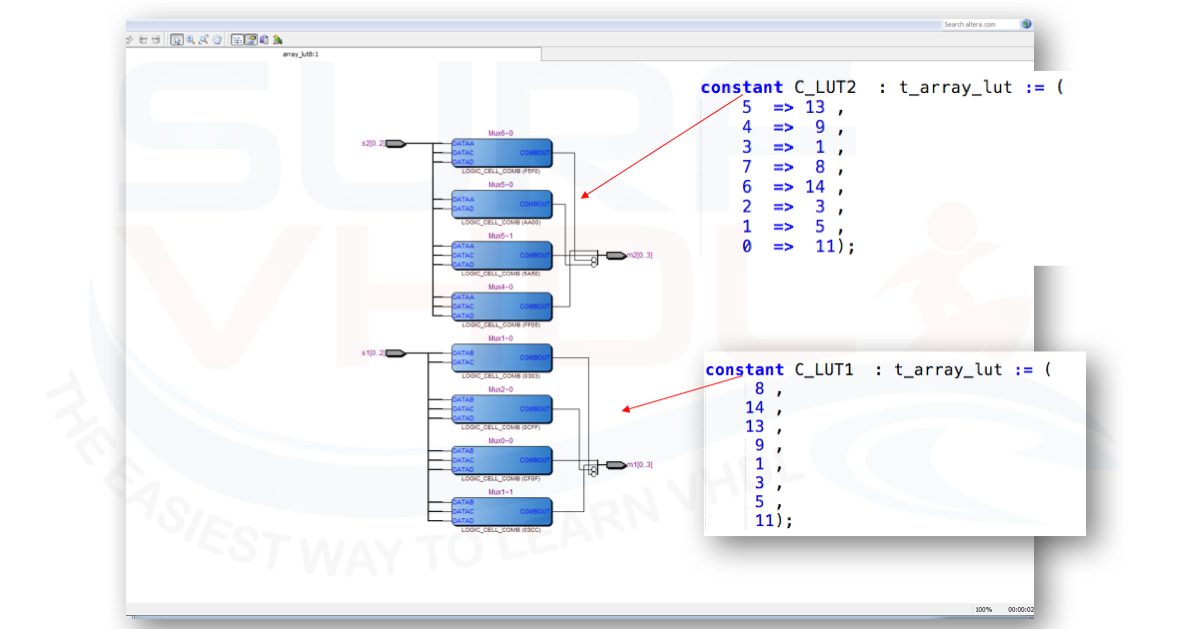

Implementing a LUT using an array in VHDL

A typical application of array in VHDL is the implementation of a LUT aka Look Up Table. In the example below is reported a vector of integer whose range is 0 to 15 i.e. 4 bit unsigned. The LUT is can be initialized in different ways as in the VHDL example below:

Figure 3 shows the technology view of the LUT implementation on Altera/Intel Cyclone II FPGA

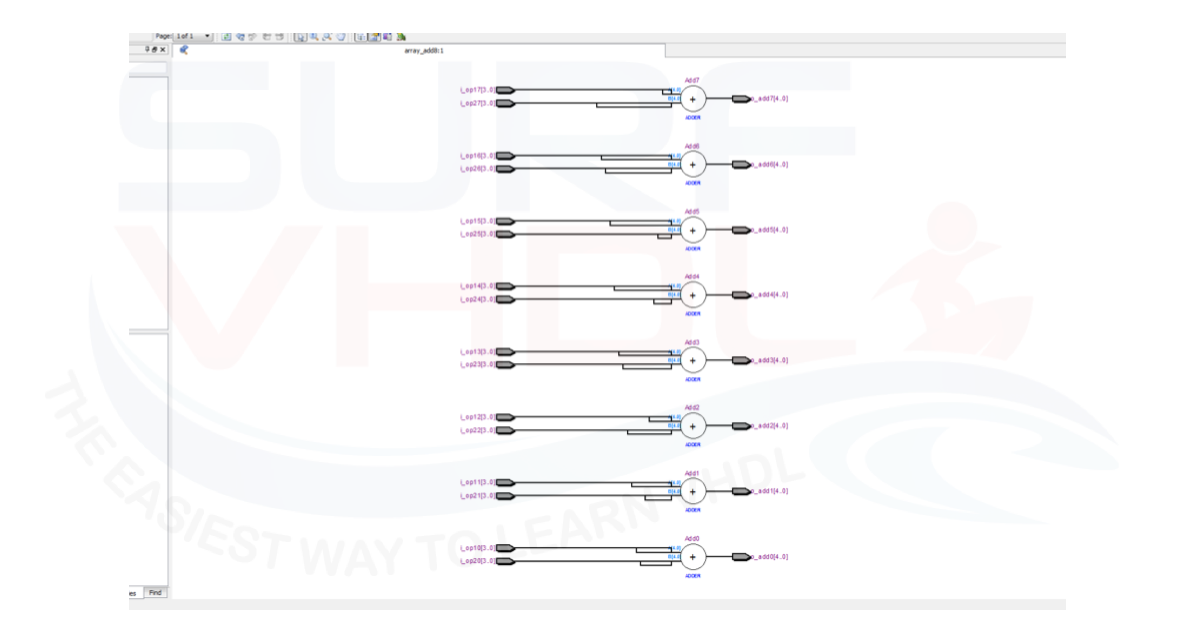

Implementing a Digital Signal Processing section using an array

Another typical example of array usage is when you need to perform the same operation on a large number of a signal. An example is adding two sets of input number in the code below:

Figure 4 shows the RTL view of the 8-adder implementation on Altera/Intel Cyclone II FPGA using the array approach.

As you saw in the previous example, using array allow you writing a very compact and elegant VHDL code. Moreover, using array approach you minimize the coding error since the VHDL code is more compact and simple to read and understand. After all these advantages, you should pay a great attention to your VHDL. Using the array coding style, you can fill a huge FPGA with only just few line of VHDL code! The rule is always the same:

Think hardware!

Every time you write a VHDL code, check the area report if it matches with your design intention and when you are not sure of the VHDL synthesis, check the RTL viewer and technology view.

[1] RTL HARDWARE DESIGN USING VHDL Coding for Efficiency, Portability, and Scalability

[2] VHDL Programming by Example 4th Ed Douglas – Perry

[3] The VHDL Cookbook

[4] Altera/Intel Cyclone II

[5] Altera Quartus II

12 thoughts to “VHDL Array”

How realize interleave array? Thanks.

Hi Valentin, can you explain better your needs?

I have a 1D array. I need to get 2 arrays: 1st – indexes 0,2,4,…, 2nd – indexes 1,3,5,…

you can use a single array and use the index (2*i) and (2*i+1)

Hello, Firstly thanks very much for your post and i found it very helpful. My questions is my input is an array of 13X13 8 bit vector and i feel wrong to simply type 169 lines for my input. Is there another way of easier definition in Entity regarding arrays as input or output?

Thanks in advance

You can use a package where define your input type. For instance:

type t_my_input_row is array(0 to 12) of std_logic_vector(7 downto 0); type t_my_input is array(0 to 12) of t_my_input_row;

your input/output port could be

my_input : in t_my_input;

Any hint on how to develop a square root synthesizable design? Thanks,

You can use a Cordic

In the first picture of the array example, vector(2)<=42 is on the 4rd element with index 3. Shouldn't it be 3rd element and index 2?

you are right, it is a typo, I’ll fix it thank you

In the Implementation of a LUT using an array in VHDL, you have written m1 <= std_logic_vector(to_unsigned(C_LUT1(to_integer(unsigned(s1))),4)); This statement I don't understand. Can you explain it more clearly?

the first type casting is “std_logic_vector” is related to m1 signal type to_integer(unsigned(s1) is related to convert to integer the signal s1

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Flexible and High-Quality VHDL programming

Array – basics

- October 18, 2019 December 26, 2019

- Keywords , VHDL Types

Array, a collection of values of the same type, is very useful representation of data in VHDL. It is helpful during creating memory blocks (FIFOs, shift registers, RAM, ROM) or in designs where exist duplicated data flows, pipes or blocks (many ADC channels, filters etc). They can be used in synchronous designs as well as in combinational. But using it in combinational parts, sometimes for specific solution, it is very important to be aware how the code will be interpreted and synthesized.

To use the array object in the code, we need to do following steps:

- declare a new type

- declare signal of a new type

- use it properly in the code

Array declaration

type array_type_name is array (elements_range) of elements_type;

array_type_name – name of a new array type, elements_range – number of elements in the array, elements_type – type of each element in the array.

Example of usage

This line creates a new array type with 4 elements, where every element is a 12-bit width std_logic_vector type:

type arr_adcin is array (0 to 4-1) of std_logic_vector (12-1 downto 0);

After declaring a new type, we can create signals of a new type:

signal signal_name : arr_adcin;

At the end, the new signal can be used in a project. Below, basic example shows how to do that.

As can be seen, it is much easier to create many identical data flows with an array type. Array usage is similar as in high-level languages. Every cell of an array is easily accessible by index value. Every cell can be used separately. With arrays, the code is much cleaner and more understandable.

Please, by aware that array itself does not optimize anything (timings or resources) but makes code much more readable and flexible (and that is what I always fight for). Array does not create any registers. It just groups similar single signals, which makes them easier to use.

*** *** ***

All source codes used in that post (with testbench) you can find on gitlab.com .

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

- Search forums

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Welcome to EDAboard.com

Welcome to our site edaboard.com is an international electronics discussion forum focused on eda software, circuits, schematics, books, theory, papers, asic, pld, 8051, dsp, network, rf, analog design, pcb, service manuals... and a whole lot more to participate you need to register. registration is free. click here to register now..

- Digital Design and Embedded Programming

- PLD, SPLD, GAL, CPLD, FPGA Design

How to declare and define 2D array in VHDL?

- Thread starter sivamit

- Start date Nov 5, 2006

- Nov 5, 2006

Full Member level 4

Hi how to declare and define 2D array in VHDL language. type dataout is array (6 downto 0,11 downto 0) of std_logic;-is this correct? But I dont know how to initialize this like a[0][1]=,a[0][2]= in C language. Please help.

- Nov 6, 2006

Advanced Member level 3

2d array vhdl Ur 2D array declaration is correct.. Code: type dataout is array (6 downto 0,11 downto 0) of std_logic; Initialization and use.. Code: library ieee; use ieee.std_logic_1164.all; entity test is end test; architecture behave of test is type dataout is array (6 downto 0,11 downto 0) of std_logic; signal a : dataout := ("000000000000", "000000111111", "101010101010", "010101010100","111111111111","111111000000","111001100110"); signal b : std_logic; begin -- behave process begin -- process for i in 0 to 6 loop for j in 0 to 11 loop b <= a(i,j); wait for 5 ns; end loop; -- j end loop; -- i wait; end process; end behave;

salma ali bakr

Full member level 2.

vhdl multidimensional array a 2d array can also be defined as follows. type dataout is array (0 to 6) of std_logic_vector(0 to 7); or type dataout is array (0 to 6)of std_logic_vector(7 downto 0); cheers,

array declaration in vhdl but can it be declared like this type Byte is array (7 downto 0) of std_logic; type dataout is array (15 downto 0) of Byte; isn't that also regarded also as a two dimensional array??? or a 1D array of a 1D array???

Member level 1

vhdl array initialization hi, can i declare a 2D array as following ? type dataout is array (6 downto 0,11 downto 0) of std_logic_vector(7 downto 0); the element is std_logic_vector not std_logic thanks

addn said: hi, can i declare a 2D array as following ? type dataout is array (6 downto 0,11 downto 0) of std_logic_vector(7 downto 0); the element is std_logic_vector not std_logic thanks Click to expand...

- Nov 7, 2006

multidimensional array in vhdl hi, maybe VHDL support 1D,1D*1D,2D but not 2D*1D

Similar threads

- Started by irfanraina1@123

- Feb 27, 2024

- Started by Lightning89

- Feb 14, 2024

- Started by nelky22

- Mar 16, 2024

- Started by Xenon02

- Jan 21, 2024

- Replies: 18

- Started by Raeiu

- Jan 19, 2024

Part and Inventory Search

Welcome to edaboard.com.

- This site uses cookies to help personalise content, tailor your experience and to keep you logged in if you register. By continuing to use this site, you are consenting to our use of cookies. Accept Learn more…

VHDL Record, Array and Custom Types

In this post, we talk about the methods we can use to create our own custom data types in VHDL , including arrays and record types.

In the previous post we talked about the basic predefined types in VHDL . Whilst these are adequate for the majority of cases there are occasions when we require a custom data type in our code.

In VHDL, the most commonly used custom types are the enumerated types. These provide us with a technique for creating an entirely new type with custom values.

However, we can also create sub types which allow us to modify the range of values in one of the predefined VHDL types. In fact, the inbuilt VHDL positive and natural types are both example of subtypes which limit the range of values the integer can accept.

In addition to this, we can also use array and record types in our VHDL designs. This can provide us with a more structured design which is easier to maintain.

In the rest of this post we will at the methods we use to create all of these custom types in our VHDL code.

Creating Custom Types

When we write VHDL code, there are instances when the predefined types we wish to create a new type. One of the most common use cases is creating an enumerated type which we us to implement finite state machines (FSM) .

Actually there are two ways in which we can create a custom type in VHDL. We can either create an entirely new type or we can create a subtype .

Let's take a look at both of these methods.

- Type Declaration in VHDL

It is possible for us to create an entirely new type to use in our VHDL design. To do this, we must create a new name for our type and then associate some valid values with it.

The code snippet below shows the general syntax we use to create an new type.

The list of values is a comma separated list of all the values of our type can have.

When declaring a new type in VHDL we typically create an enumerated type. This means our list of values are just strings, or words, which we can assign to any instances of the type.

As an example, let's create a new type which we use to store the state of a small FSM. This is one of the most common reasons for creating a new type in VHDL.

For this example, our FSM will have just four states - idle, starting, runnning and stopping.

The code snippet below shows how we would create this type in VHDL. We can see that this is an enumerated type, meaning the list of values are simple strings.

Once we have created this type, we can create an instance of it in our code. We can then assign any value to it which we have listed in the declaration.

The code snippet below shows how we would create a signal using our custom type and assign it to the idle state.

- Subtype in VHDL

The second method we can use to create a custom type modifies one of the existing types. To do this, we use the subtype VHDL keyword and restrict the range of valid values which the new type can take.

The code snippet below shows the general syntax we use when creating a sub type.

One of the most common uses for the sub type keyword in VHDL is to restrict the number of bits in an integer type.

As an example, we may want to declare an integer which only uses 8 bits. In this case we can declare a new subtype and limit the maximum value to 255. The code snippet below shows how we would do this.

After we have created a new subtype, we can create instances of it to use in our VHDL design. We can then assign it any of the values we specified in the declaration.

The code snippet below shows how we would create a signal using our new type.

- Creating Array Types in VHDL

We can create our own array types in VHDL. To do this, we include the array keyword in the type definition. We must also declare the number of elements in the array.

The code snippet below shows the general syntax we use to declare an array type in VHDL.

The <type> field in the above construct can accept any VHDL type, including custom types we have declared. This means we can also build multidimensional arrays by using array types in this field.

The <range> field in the above example can be built using the downto and to VHDL keywords which we have seen before.

However, we can also use two special constructs which effectively create an unconstrained array type. This allows us to define the size of the array whenever we declare a port or signal which uses it.

To do this, we use the natural <range > or positive <range> keywords in the <range> field. The difference between the two is that the natural <range> option allows for zero based array numbering whereas positive <range> doesn't.

The VHDL code below shows the general syntax we use to create unconstrained array types.

Once we have declared a custom array type it can be used in an entity port, as a signal or a as a variable.

- An Example Array Type

To demonstrate how we declare a custom array type, lets consider a basic example. For this example we will create an array of 8 bit std_logic_vector types.

In addition, we will not constrain the array when we declare it. Instead, we will use the natural <range> construct so that we can change the size as we declare signals.

The code snippet below shows how we declare and use our custom array type.

Record Type in VHDL

We can create more complex data types in VHDL using a record. Records can contain any number of different signals which we want to group together. These signals don't need to be of the same type.

We can think of records as being roughly equivalent to structs in C.

We often use records to simplify the port list in a VHDL entity . If we have a number of common signals, we can group them together in a record. We can then use this record as part of the entity which reduces the number of ports we require.

Using record types in an entity can also improve the maintainability of our code. The main reason for this is that we only need to manage the contents of a record in the place it is declared. Therefore, we can change connections in our ports just by modifying the record type. If our design features multiple modules which use the same record, this can reduce the effort require to modify connections between entities.

- Declaring and Using a Record in VHDL

When we want to use a record in VHDL we must declare it as a type. We most commonly declare records inside a VHDL package . This allows us to use the record type in multiple different design files.

The code snippet below shows the general syntax we use to declare a record type in VHDL.

After we have declared a record type, we can use it in the exact same manner as any other port or signal in our VHDL design. We can assign data to individual elements in the record or to the entire array.

The code snippet below shows the two methods we can use to assign data to the record.

It is also possible for us to include records as elements in an array.

- An Example Record Type

Lets consider a basic example to better demonstrate how a record type works in VHDL. For this example, we will write a record which contains all the signals required in a UART interface.

The UART interface consists of 4 different signals. Each of these signals are a single bit which means we can use a std_logic type to model them.

The code snippet below shows how we would declare this record type.

After we have created the record, we can then use it in the type field for any port or signal in our VHDL design.

The code snippet below shows hows we would declare a signal which uses our UART record type.

Finally, we will obviously also want to drive data onto our record signal. The VHDL code snippet below gives some examples of how we can assign data to the record.

Write some VHDL code which creates an enumerated type for an FSM. The FSM has 4 states – idle, running, stopped and error

Create an integer subtype which can have a value between 5 and 200.

Write some VHDL code which declares an array of 8 32-bit std_logic_vectors

Write a record type which consists of an 8 bit unsigned type, a std_logic type and an unconstrained integer.

Table of Contents

Sign up free for exclusive content.

Don't Miss Out

We are about to launch exclusive video content. Sign up to hear about it first.

IMAGES

VIDEO

COMMENTS

Arrays - VHDL Example Create your own types using arrays. Arrays are used in VHDL to create a group of elements of one data type. Arrays can only be used after you have created a special data type for that particular array. Below are some rules about arrays. Arrays can be synthesized; Arrays can be initialized to a default value

13. in a 2D array e.g.: type lutable is array (0 to 4, 0 to 2) of integer range 0 to 4000; signal sample_array: lutable; you can assign elements to another signal as follows: out_signal<=sample_array(in_a, in_b); the contents of the array can be declared e.g. as defaults (caution, this is not supported by all synthesis-tools!):

Arrays are a collection of a number of values of a single data type and are represented as a new data type in VHDL. ... VHDL does not put any restrictions on the index set of arrays, as long it is a discrete range of values. ... The most convenient way to assign values to multiple array elements is via the aggregate mechanism. Aggregates can ...

Arrays - VHDL Example Create your own types using arrays. Arrays are second in VHDL to create a group of elements of one data type. Arrays bottle only be used after you have created a special data type for such particular array. Down are more rules info dresses. Strange but useful construct: type'(others => '0')

The VHDL Fields reference syntax and VHDL Array initialization. One and Multi-dimensional VHDL array. Arrays can be synthesized; Arrays can be initialized to a default value; Array type definitions can be unconstrained (undefined length) Arrays of arrays were permissible (e.g. an array of std_logic_vector) Two-Dimensional (2D) arrays are allowed

Field are used in VHDL to create an group of elements of one data type. Arrays can single will used subsequently you have created a special data type for that especially array. Below are some rules about arrays. Synthesizable multidimensional arrays in VHDL. Arrays can be synthesized; Arrays bucket be initialized to a default value

An array contains multiple elements of the same type. When an array object is declared, an existing array type must be used. An array type definition can be unconstrained, i.e. of undefined length. String, bit_vector and std_logic_vector are defined in this way. An object (signal, variable or constant) of an unconstrained array type must have ...

@drjohnsmith (Member) 2008 not needed. Both code examples are VHDL 1993 code. @Eze (Member) While both are legal, neither will infer a RAM in Vivado. You need to use a 1d array to infer a ram. So you will need to do the following: type ram_t is array (0 to MEM_DEPTH * (2 ** CHANNEL_WIDTH)-1) of std_logic_vector (DW-1 downto 0); signal ram : ram_t;--in a clocked process etc, following synthesis ...

Ranges - VHDL Example Creation will own types use arrays. Arrays are often in VHDL to create a group from default of one data type. Arrays can only be used after you have created a special data type for that particular array. Below are of rules about arrays. Arrays can is synthesized; Arrays can be initialized at a default value

2. In the VHDL code segment shown below, determine the value assigned. Write a VHDL declaration for an array initial values are x"4" and x"7". range that has the same limits as z. 3. Write a VHDL procedure minMax that takes two eight bit inputs and.

In VHDL such kind of structure is defined " array ". We can collect any data type object in an array type, many of the predefined VHDL data types are defined as an array of a basic data type. An example is: type string is array (positive range <>) of character; type bit_vector is array (natural range <>) of bit; Figure 1 - example of VHDL ...

Array - basics. Array, a collection of values of the same type, is very useful representation of data in VHDL. It is helpful during creating memory blocks (FIFOs, shift registers, RAM, ROM) or in designs where exist duplicated data flows, pipes or blocks (many ADC channels, filters etc). They can be used in synchronous designs as well as in ...

2d array in vhdl yah like nandgates said u have to declare a signal from the type you made and put the initialization values for it but take care,you can only reference:-the whole array --> array_2D-a single element of the array --> array_2D(1,1) or array_2D (2,3) or whatever

We can create our own array types in VHDL. To do this, we include the array keyword in the type definition. We must also declare the number of elements in the array. The code snippet below shows the general syntax we use to declare an array type in VHDL. type <type_name> is array (<range>) of <type>;

The term aggregate mean "collection". That is true for the right hand side of an assignment, but not for the left hand side (LHS). The LHS is the reverse operation - a split operation. It is called decomposition or unpacking. The correct way in the VHDL LRM would be to have a e.g. decomposition BNF rule, that is an alias for the aggregate rule.

I want to use a 2D array in a Verilog testbench. I tried it this way: module tb; reg [7:0] DataToSend [0:7] = {8'h01, 8'h10, 8'h22, 8'h32, 8'h55, 8'hAA, 8'hAB, 8'h88}; endmodule ... An n-bit reg can be assigned a value in a single assignment, but a complete memory cannot. To assign a value to a memory word, an index shall be specified. Most ...

Addenda: Each record in the 2D array looks like: enable : std_logic; index : std_logic_vector(7 downto 0); cmd : std_logic_vector(2 downto 0); So I will have interfaces like these in a row-column arrangement: I will need to break-out the record signals by the column (using a multiplexer).

\$\begingroup\$ You cannot have arrays of unknown size. It's a hardware description language, everything has a size. So figure out what's the maximum size of your array. Either use one of your 4 values as empty/unused or define a fivths value or return a second parameter size/length like in C. \$\endgroup\$

1. This is because VHDL is a stronly typed language. Here rx_ram and Q1_ram are different types, and hence cannot be directly assigned to one another. Even more difficult, because you have assigned a size to your types, you cannot do a type conversion because the slices have no distinct type that can be named for a closely related type conversion.