Verilog Inter and Intra Assignment Delay

Verilog delay statements can have delays specified either on the left hand side or the right hand side of the assignment operator.

Inter-assignment Delays

An inter-assignment delay statement has delay value on the LHS of the assignment operator. This indicates that the statement itself is executed after the delay expires, and is the most commonly using form of delay control.

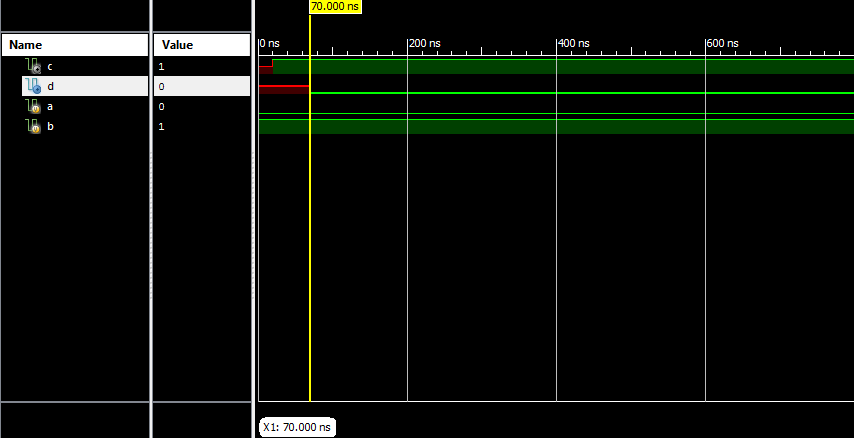

Note that q becomes 1 at time 10 units because the statement gets evaluated at 10 time units and RHS which is a combination of a , b and c evaluates to 1.

Intra-assignment Delays

An intra-assignment delay is one where there is a delay on the RHS of the assignment operator. This indicates that the statement is evaluated and values of all signals on the RHS is captured first. Then it is assigned to the resultant signal only after the delay expires.

Note that the assignment to q is missing in the log !

This is because at 5 time units, a and c are assigned using non-blocking statements. And the behavior of non-blocking statements is such that RHS is evaluated, but gets assigned to the variable only at the end of that time step.

So value of a and c is evaluated to 1 but not yet assigned when the next non-blocking statement which is that of q is executed. So when RHS of q is evaluated, a and c still has old value of 0 and hence $monitor does not detect a change to display the statement.

To observe the change, let us change assignment statements to a and c from non-blocking to blocking.

Delay in Assignment (#) in Verilog

Syntax : #delay

It delays execution for a specific amount of time, ‘delay’.

There are two types of delay assignments in Verilog:

Delayed assignment: #Δt variable = expression; // “ expression” gets evaluated after the time delay Δt and assigned to the “variable” immediately Intra-assignment delay: variable = #Δt expression; // “expression” gets evaluated at time 0 but gets assigned to the “variable” after the time delay Δt

Note: #(delay) can not be synthesized. So we do not use #(delay) in RTL module to create delay. There are other methods which can be used to create delays in RLT module. #(delay) can be used in testbench files to create delays.

Spread the Word

- Click to share on Facebook (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on LinkedIn (Opens in new window)

- Click to share on Pinterest (Opens in new window)

- Click to share on Tumblr (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to share on Reddit (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

Related posts:

- Blocking (immediate) and Non-Blocking (deferred) Assignments in Verilog

- Ports in Verilog Module

- Synthesis and Functioning of Blocking and Non-Blocking Assignments.

- Module Instantiation in Verilog

Post navigation

Leave a reply cancel reply.

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Notify me of follow-up comments by email.

Notify me of new posts by email.

- The Verilog-AMS Language

- Continuous Assigns

Continuous Assigns

A module may have any number of continuous assign statements. Continuous assign statements are used to drive values on to wires. For example:

This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire. The continuous assign statement is not a procedural statement and so must be used at the module level; it cannot be placed in an initial or always process.

You can add delay to a continuous assign statement as follows:

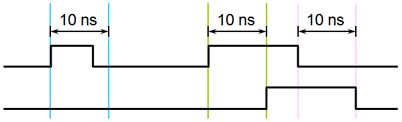

In this case, the value of a changes 10 units of time after the expression b & c changes. Continuous assign statement implement inertial delay, meaning that continuous assign statements swallow glitches. This is illustrated below with the assumption that the unit of time is 1ns.

It is possible to specify up to three delay values on a continuous assignment:

When you specify more than one:

The first delay refers to the transition to the 1 value (rise delay).

The second delay refers to the transition to the 0 value (fall delay).

The third delay refers to the transition to the high-impedance value.

When a value changes to the unknown (x) value, the delay is the smallest of the delays specified.

If only two delays are specified, then the delay to high-impedance is the smallest of the two values specified.

- Timing Control

Quick links

- Introduction to Chip Design Process

- Description of Hardware Description Languages

- Design Methodology

- Verilog HDL Design Flow

- Introduction to Modeling

- Gate Delays

- Delays in Dataflow modelling

- Different types of Behavioral modeling

- Conditional Statements

- Procedural Continuous Assignment

- User-Defined Primitives

- Useful System Tasks

- Switch Level Modeling style

- Traffic Light Controller

- Shift Unit Design

- MISR (Multiple input signature register)

- Introduction to FPGA & CPLD

- LED Interfacing with FPGA

In our last blog, we studied different types of statements. Let’s discuss today the another part.

Verilog provides a number of behavioural timing control mechanisms. The simulation time in Verilog does not advance if there are no timing control statements.

Timing settings allow you to select the simulation time when procedural statements will be executed.

Timing control may be done in three ways: delay-based timing control, event-based timing control, and level-sensitive timing control.

Delay-based Timing Control

In the earlier blogs, we utilised delay-based timing control statements but did not describe them in depth.

In an expression, delay-based timing control provides the time interval between when the statement is encountered and when it is performed.

We’ll talk about delay-based timing control statements in this section. This # symbol represents delays. The delay-based timing control statement’s syntax is presented below.

<delay>

: := #<NUMBER>

| | = #<identifier>

| | = #(<mintypmax_expression> <,<mintypmax_expression>>*)

A number, an identifier, or a mintypmax expression can be used to specify delay-based timing control.

For procedural assignments, there are three forms of delay control: normal delay control, intra-assignment delay control, and zero delay control.

Inter delay control

When a non-zero delay is supplied to the left of a procedural assignment, inter delay control is employed.

Intra-assignment delay

When a delay can be specified to the right of the assignment operator, This type of delay specification changes the flow of activities in a different way.

Take note of the distinction between intra-assignment and inter delays from above examples. Inter delays postpone the completion of the entire task.

Intra-assignment delays compute the right-side expression at the present time and postpone the assignment of the computed value to the left-side variable.

Intra-assignment delays are analogous to utilising inter-assignment delays in conjunction with a temporary variable to hold the current value of a right-hand-side expression.

Zero delay control

At the same simulation time, procedural statements in distinct always-initial blocks may be examined. The sequence in which these statements are executed in separate always-initial blocks is nondeterministic.

Zero delay control is a technique for ensuring that a statement is performed after all other statements in that simulation time have been executed.

Event-based Timing Control

A change in the value of a register or a net is referred to as an event. Events can be used to initiate the execution of a statement or a set of statements. Event-based timing control is classified into four categories. Regular event control, named event control, event OR control, and level-sensitive timing control are all types of event control.

Regular event control

Statements can be executed when the signal value changes or when the signal value transitions from positive to negative. The “#” symbol represents an event control.

Named event control

You can specify an event, then trigger and identify its occurrence. The event has no data. The keyword event declares a specified event.

The ” ->” symbol causes an event to occur. The event’s triggering is indicated by the sign “@”.

Event OR control

A transition on any of several signals or events can sometimes cause the execution of a statement or a block of statements.

This is stated as an OR of event or signals. A sensitivity list is a set of events or signals expressed as an OR.

Level-sensitive timing control

The earlier described event control waited for a change in a signal value or the triggering of an event. Edge-sensitive control was given by the symbol.

Verilog also supports level-sensitive timing control, which allows you to wait for a condition to be true before executing a statement or a block of statements. For level-sensitive constructions, the keyword “wait” is used.

The value of count_enable is continually noted in the example.

If count_enable is zero, the statement is skipped. If it is logical 1, the expression count = count + 1 is performed 20 time units later. If count enabled is set to 1, the count will be increased every 20 units.

So, after reading this blog today, we learnt about timing controls and their many sorts. To summarise this blog, here are some questions you may simply answer.

- What is timing control and what are its many types?

- What exactly is delay-based timing control, and how many different forms of delay-based timing control exist?

- What is the distinction between normal and intra-assignment delay?

- What is event-based timing control and what are its many types?

- What precisely is level-sensitive timing control?

Please Login or Register to comment on this post

Only fill in if you are not human

Recent Blogs

Loop statement, procedural assignment, data type, typedef methods.

- Privacy Policy

- @VLSI_Master

- VLSI-Master

Copyright © 2021 All rights reserved

IMAGES

VIDEO

COMMENTS

An intra-assignment delay is one where there is a delay on the RHS of the assignment operator. This indicates that the statement is evaluated and values of all signals on the RHS is captured first. Then it is assigned to the resultant signal only after the delay expires. module tb;

Syntax: #delay. It delays execution for a specific amount of time, ‘delay’. There are two types of delay assignments in Verilog: Delayed assignment: #Δt variable = expression; // “ expression” gets evaluated after the time delay Δt and assigned to the “variable” immediately.

Adding delays to the left hand side (LHS) of any sequence of blocking assignments to model combinational logic is also flawed. The adder_t7a example shown in Figure 4 places the delay on the first blocking assignment and no delay on the second assignment. This will have the same flawed behavior as the adder_t1 example.

The Verilog intra assignment delay does not seem to work as I wanted. I am trying to model an OR gate with an output delay of 2 NS. Design: module or_gate(input a, b, output logic g); always@(*) begin g = #2 a | b; end endmodule Testbench:

Continuous assign statements are used to drive values on to wires. For example: assign a = b & c; This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire.

SNUG Boston 2002 Verilog Nonblocking Assignments Rev 1.4 With Delays, Myths & Mysteries 44 11.6 The 20,000 flip-flop benchmark with #1 delays in the I/O flip-flops All of the preceding mixed RTL and gate-level simulation problems can be traced to signals becoming skewed while crossing module boundaries.

Blocking Assignment. A blocking assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; It is also possible to add delay to a blocking assignment. For example: a = #10 b + c; In this case, the expression on the right hand side is evaluated and the value ...

The a is assigned to x at simulation time 5, while b is assigned to y at simulation time 10. Now consider nonblocking assignment statements with intra-assignment delays that follow in a sequential block: initial begin. x<=#5 a; y<=#5 b; end. In the above case both a and b are concurrently assigned to x and y at simulation time 5.

Verilog provides a number of behavioural timing control mechanisms. The simulation time in Verilog does not advance if there are no timing control statements. Timing settings allow you to select the simulation time when procedural statements will be executed. Timing control may be done in three ways: delay-based timing control, event-based ...